“3D堆叠”推动半导体继续进化

2022/04/12

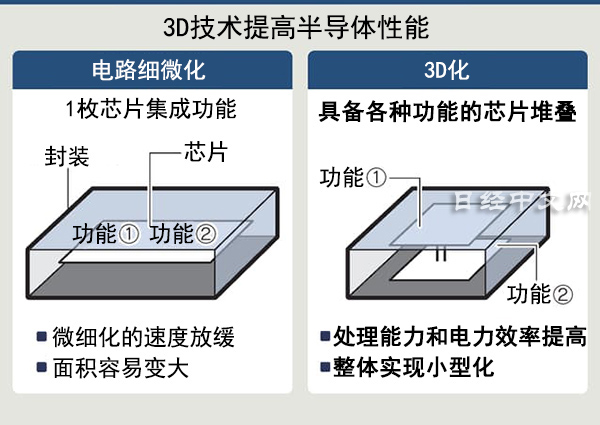

在用于个人电脑和高性能服务器的尖端半导体开发方面,三维(3D)堆叠技术的重要性正在提高。在通过缩小电路线宽提高集成度的“微细化”速度放缓的背景下,3D技术将承担半导体持续提高性能的作用。台积电(TSMC)、英特尔等半导体大型企业以及日本的设备和材料厂商等正在竞相展开技术开发。

|

临时存储容量增至3倍

1月,美国超微半导体公司(AMD)在世界最大的电子产品消费展“CES”上推出的个人电脑CPU(中央处理器)受到半导体行业的关注,“我们非常兴奋能为大家提供配备3D技术的产品”。

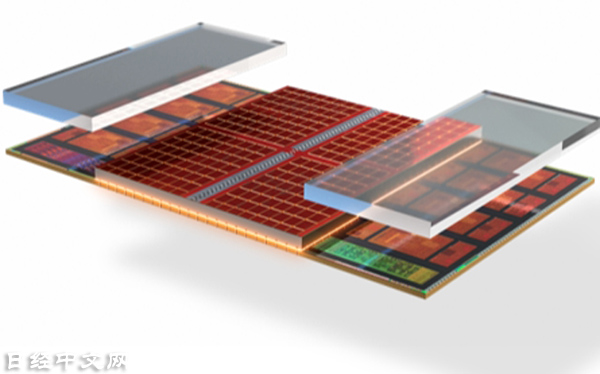

特征在于其结构。通常是在相同硅基板上实现的运算和临时存储功能,但AMD的产品是由2枚不同的芯片分别承担功能,在1个封装内纵向叠加。这样一来,临时存储的容量提高到通常的3倍,游戏芯片的处理性能比此前产品提高了15%。AMD计划将3D技术应用于服务器CPU。

|

| AMD在个人电脑CPU等产品上采用了3D技术 |

在过去约50年里,半导体性能提高的主角是在1个硅基板上嵌入大量微小电路的微细化。根据性能在18个月~2年内提高2倍的“摩尔定律”,微细化技术持续发展。英特尔1971年发布的首款CPU的元件数仅有约2300个,苹果最新发布的“M1”芯片元件数达到160亿个,增至约700万倍。但是,进入2010年代后,线宽接近原子的尺寸,微细化的速度开始放缓。

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。报道评论

金融市场

| 日经225指数 | 28493.47 | 336.50 | 04/14 | close |

| 日经亚洲300i | 28493.47 | 336.50 | 04/14 | close |

| 美元/日元 | 132.42 | -0.60 | 04/14 | 15:15 |

| 美元/人民元 | 6.8381 | -0.0298 | 04/14 | 07:14 |

| 道琼斯指数 | 34029.69 | 383.19 | 04/13 | close |

| 富时100 | 7843.380 | 18.540 | 04/13 | close |

| 上海综合 | 3336.1530 | 17.7892 | 04/14 | 14:05 |

| 恒生指数 | 20405.12 | 60.64 | 04/14 | 14:04 |

| 纽约黄金 | 2041.3 | 30.4 | 04/13 | close |

・日本经济新闻社选取亚洲有力企业为对象,编制并发布了日经Asia300指数和日经Asia300i指数(Nikkei Asia300 Investable Index)。在2023年12月29日之后将停止编制并发布日经Asia300指数。日经中文网至今刊登日经Asia300指数,自2023年12月12日起改为刊登日经Asia300i指数。