“3D堆叠”推动半导体继续进化

2022/04/12

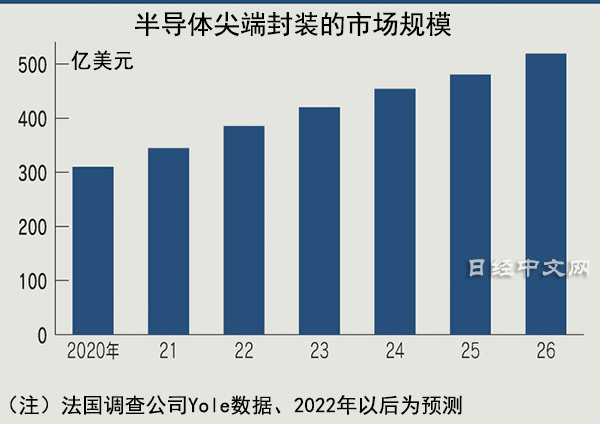

法国调查公司Yole预测称,包括3D等技术在内的尖端半导体封装的2026年市场规模将增至2021年的1.5倍,达到519亿美元。随着技术创新,半导体领域将诞生新的火车头,相关市场也有望扩大。

|

标准化组织确保兼容性,推动新合作

半导体3D化的优点不仅限于持续提高性能。新形式的分工和合作或将取得进展。

尖端半导体的制造成本随着技术的升级,正在滚雪球般膨胀。如果采用多枚芯片分担功能的3D技术,“核心部分的芯片采用尖端进程,而周边部分采用非尖端技术,有可能降低制造成本”,行业相关人士表示。

将来,设想将不同公司设计和制造的芯片纳入相同的封装,作为1个产品使之发挥功能。英特尔、台积电和三星电子等半导体巨头于3月2日成立了芯片互连的标准化组织。谷歌、微软和Meta等美国IT企业也加入了组织。

索尼集团在主力的图像传感器上最先开始采用3D技术。有分析师指出,索尼在获取光像素和逻辑芯片的堆叠上采用铜的自主布线技术,“这是与(在熊本县合资建厂的)台积电合作上的关键技术”。

如果将各种芯片结合起来的3D技术得到普及,专注于设计的无厂半导体厂商之间、以及与后工序代工企业等的合作将提高重要性。以3D半导体的开发和制造技术为核心,半导体厂商的行业势力版图有可能发生改变。

日本经济新闻(中文版:日经中文网)龙元秀明 佐藤雅哉

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。

报道评论

金融市场

| 日经225指数 | 28493.47 | 336.50 | 04/14 | close |

| 日经亚洲300i | 28493.47 | 336.50 | 04/14 | close |

| 美元/日元 | 132.42 | -0.60 | 04/14 | 15:15 |

| 美元/人民元 | 6.8381 | -0.0298 | 04/14 | 07:14 |

| 道琼斯指数 | 34029.69 | 383.19 | 04/13 | close |

| 富时100 | 7843.380 | 18.540 | 04/13 | close |

| 上海综合 | 3336.1530 | 17.7892 | 04/14 | 14:05 |

| 恒生指数 | 20405.12 | 60.64 | 04/14 | 14:04 |

| 纽约黄金 | 2041.3 | 30.4 | 04/13 | close |

・日本经济新闻社选取亚洲有力企业为对象,编制并发布了日经Asia300指数和日经Asia300i指数(Nikkei Asia300 Investable Index)。在2023年12月29日之后将停止编制并发布日经Asia300指数。日经中文网至今刊登日经Asia300指数,自2023年12月12日起改为刊登日经Asia300i指数。