半导体主角更替(上)3D技术竞赛

2022/02/18

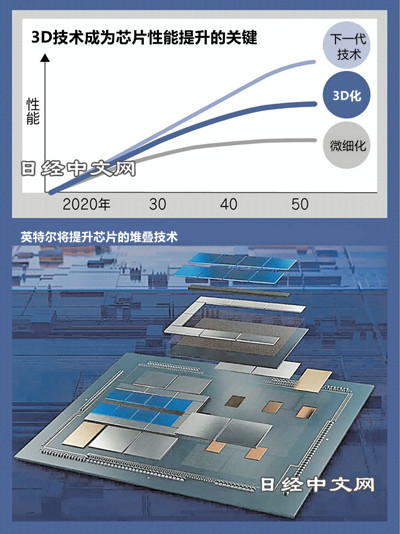

世界半导体大型企业英特尔和台积电(TSMC)等的尖端开发的情况正在改变。仅凭缩小电路线宽、提高集成度的“微细化”已不能跟上性能提高的需求,日趋需要新技术。各企业竞相开发的是将多个芯片堆叠起来,提高性能的三维(3D)技术。在半导体技术的新主角亮相的背景下,日本的设备和材料企业也在迎来商机。

“要让产品水平符合‘摩尔定律’,封装技术的升级变得重要”,2021年12月在东京发表演讲的英特尔高管佩恩·巴依(音译)呼吁日本设备和材料厂商提供协助。

摩尔定律是意为半导体性能在18个月~2年里提高至2倍的“经验法则”。实际上,在半个多世纪里,一直维持法则所预示的性能提高。起到牵引作用的是微细化技术,一直使电路变得更细,装入更多用于运算等的元件。

|

以美国苹果公司使用的半导体为例,2020年采用的芯片处理晶体管达到118亿个,在1年里增加逾30亿个。归根结底,一直支撑智能手机等飞跃式升级的也是微细化。

微细化笼罩阴影

这种微细化的速度已开始笼罩阴影。最细小的电路线宽为十多纳米(纳米为10亿分之1米)。要描绘更加微细的电路,物理上的制约明显,制造和开发所需的成本有可能超过性能提高的优点。

目前在运算等方面,有不使用电子、而利用光子的“光电融合”,以及晶体管结构变化等有望实现飞跃式发展的新一代技术。不过,在处理庞大信息的数据驱动型社会,如果运算能力的提高停止,耗电量将无限度上升。

要支撑最终产品的进步和数据社会,半导体性能的持续提高是不可或缺的。作为目前的方案,各企业关注的是借助多个芯片提高集成度的3D堆叠技术。

台积电正加快开发名为“3DFabric”的3D结构半导体,在日本茨城筑波市设置具有研发功能的机构也是战略一环。台积电日本3DIC研发中心的负责人江本裕表示,为了发展3D堆叠技术,“材料、设备企业等生态系统的协助不可或缺”。

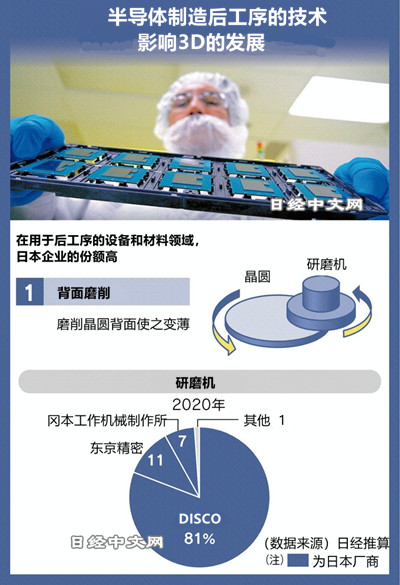

成为关键的后工序

要使半导体芯片在3D方向上集成并加以驱动,必须解决热和电流等问题。关键是从晶圆上切下半导体、加工为芯片的后工序的技术。

|

材料和设备需具备的条件严苛。江本裕表示“基板的平坦度、热膨胀率和弹性等各种数值都需要优化”。一名日本国内的化学试剂企业高管表示,“难以利用目前的技术解决,需要开发面向每个客户进行个别优化的材料”。

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。

报道评论

金融市场

| 日经225指数 | 28493.47 | 336.50 | 04/14 | close |

| 日经亚洲300i | 28493.47 | 336.50 | 04/14 | close |

| 美元/日元 | 132.42 | -0.60 | 04/14 | 15:15 |

| 美元/人民元 | 6.8381 | -0.0298 | 04/14 | 07:14 |

| 道琼斯指数 | 34029.69 | 383.19 | 04/13 | close |

| 富时100 | 7843.380 | 18.540 | 04/13 | close |

| 上海综合 | 3336.1530 | 17.7892 | 04/14 | 14:05 |

| 恒生指数 | 20405.12 | 60.64 | 04/14 | 14:04 |

| 纽约黄金 | 2041.3 | 30.4 | 04/13 | close |

・日本经济新闻社选取亚洲有力企业为对象,编制并发布了日经Asia300指数和日经Asia300i指数(Nikkei Asia300 Investable Index)。在2023年12月29日之后将停止编制并发布日经Asia300指数。日经中文网至今刊登日经Asia300指数,自2023年12月12日起改为刊登日经Asia300i指数。