日本半导体重振的关键——后工序

2021/07/02

日本的半导体封装技术正受到关注。在半导体组件的微细化日益困难的背景下,通过把半导体芯片堆叠起来提升性能的“3D堆叠技术”的重要性正在提高。日本汇聚揖斐电(IBIDEN)、芝浦机电(SHIBAURA MECHATRONICS)、JSR等拥有较高技术实力的设备和材料厂商。世界最大半导体代工企业台积电(TSMC)也开始在日本启动最尖端堆叠技术的联合开发。

位于茨城县筑波市的产业综合研究所的无尘室成为力争开发新半导体技术的日台联盟的基地。

|

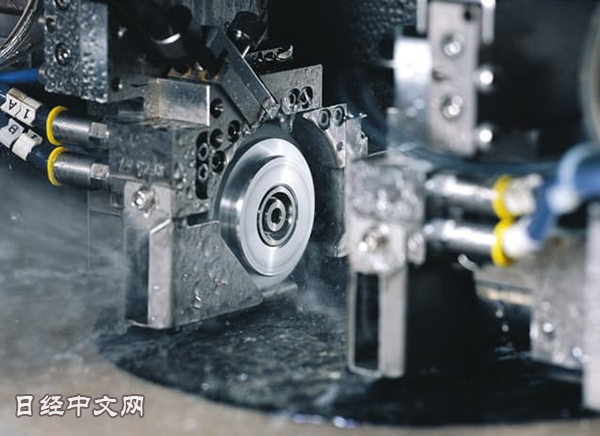

| 日本的后工序技术拥有较强的竞争力(迪思科的研发中心内) |

台积电的子公司——台积电日本3DIC研发中心(横滨市)构建了以揖斐电、JSR、迪思科等21家日本半导体相关企业为中心的联合开发体制。5月31日,一直在争取台积电的日本经济产业省发布了伙伴企业的名单。在股票市场,相关企业的股价联袂上涨。

将在筑波市联合开发的是新的3D堆叠技术。以立体形式把半导体芯片连接起来,实现高速通信和节电化。能突破在2D设计微细化的极限,提高性能。

还能把芯片之间的数据移动所需的能源减为约1000分之1,大幅减少系统整体的耗电量。有望实现数据中心的节电化以及提高人工智能(AI)性能。以台积电为代表,英特尔、三星电子等世界知名半导体厂商在3D堆叠技术的开发方面展开激烈竞争。

日本企业拥有大量3D堆叠所需关键技术。这是被称为“后工序”的制造流程需要的技术领域。指的是经过在晶圆上形成电路的“前工序”阶段后,切分为芯片、连接电极、通过树脂进行封装的技术等。

台积电2月宣布在日本建立研发基地,日本经济产业省一名高官回顾称,“如果没有揖斐电,就无法把台积电吸引到日本”。即使是台积电,要实现最尖端的3D堆叠技术,也离不开日本企业的技术。

3D堆叠需要以立体形式把半导体芯片和基板直接堆叠连接起来。要以高精度对准芯片和基板的细小端子,并进一步提高生产效率和散热性等,必须具备综合性的产品制造能力。台积电选择的合作伙伴全都是在半导体的封装和材料技术上拥有顶尖实力的企业。

在切分芯片的切割机领域,迪思科(DISCO)约占7成份额。在把芯片和基板连接起来的组装设备领域,芝浦机电能提供面向尖端封装的设备。

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。

报道评论