东芝开发新存储器能让手机省电20%

2014/06/11

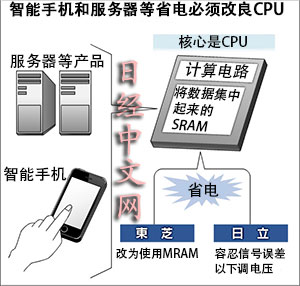

日本半导体厂商正在竞相开发可大幅减少智能手机和服务器等产品耗电量的半导体技术。东芝制作出了将半导体嵌入CPU(中央处理器)的省电存储器“磁性随机存储器(MRAM)”。日立制作所通过改变存储器的使用方法,开发出了在一定范围内容忍出现信号误差的方法。两种方法均可节省约20%耗电量。很多使用者对智能手机充满电后都用不上1天感到不满。如果省电技术得以普及,IT设备的易用性将得到改善。

CPU的耗电量占智能手机耗电量的约1/3。在CPU内部,用于存储数据的“静态随机存取存储器(SRAM)”的耗电量较大。

东芝开发出了比SRAM省电的新一代半导体MRAM。MRAM具有即使切断电源也能保持记录的特性,由通过磁力来记忆信号的元件和放大微弱信号的电路构成。东芝通过使电路靠近元件来提高处理速度,实现了毫不逊色于SRAM的性能。

东芝表示,如果推向实用化将“有望使智能手机的耗电量减少20%”。以电源待机时间为10小时的智能手机为例,其待机时间将增加到12小时。

预计MRAM作为主力存储器将替代一般的“动态随机存储器(DRAM)”。此次东芝还为MRAM替代SRAM开辟了道路。东芝计划2015财年(截至16年3月)之前开发出嵌入新型MRAM的CPU,力争实现商业化。

日立制作所面向服务器等产品开发出了在利用SRAM的同时还能省电的技术。SRAM方面,虽然可实现省电和高速化的电路细微化技术取得了发展,但是达到一定程度后很容易出现信号误差,导致SRAM的性能出现下降。过去通过施加高电压将信号误差几乎控制为零,不过该技术会影响省电效果。

日立转变了一直以来的思考方式,容忍可忽略的误差发生,开发出了可抑制SRMA驱动电源的设计方法。与系统控制有关的重要处理方面,通过软件来维持驱动电压,计算处理则根据事先设定的误差率来下调电压。

据称采用该方法计算机也能正常工作。预计还可以用于图像处理等。在模拟试验中,容忍5%的误差率的情况下,可将耗电量削减20%左右。

据称这一误差率在人观看图像时感觉不到图像出现劣化的范围内。日立计划20年将该方法推向实用,这将有助于信息社会的基础设施数据中心的节能化。

另一方面,由富士通和三菱电机等10家厂商组成的的超低电压装置技术研究联盟开发出了面向构成MRAM的记忆元件的微细加工技术。具体来说,首先制作出直径为35纳米(1纳米为10亿分之1米)的圆形元件,之后使元件周围氧化,将元件工作部分直径缩小至20纳米。

尽管微细化对实现省电有效,但是加工起来十分困难。据称相比一开始就将元件加工为直径20纳米,新技术的精确度更高、成本也更低。加入研究联盟的各厂商计划为高性能MRAM的实用化做出贡献。

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。

|

东芝开发出了比SRAM省电的新一代半导体MRAM。MRAM具有即使切断电源也能保持记录的特性,由通过磁力来记忆信号的元件和放大微弱信号的电路构成。东芝通过使电路靠近元件来提高处理速度,实现了毫不逊色于SRAM的性能。

东芝表示,如果推向实用化将“有望使智能手机的耗电量减少20%”。以电源待机时间为10小时的智能手机为例,其待机时间将增加到12小时。

预计MRAM作为主力存储器将替代一般的“动态随机存储器(DRAM)”。此次东芝还为MRAM替代SRAM开辟了道路。东芝计划2015财年(截至16年3月)之前开发出嵌入新型MRAM的CPU,力争实现商业化。

日立制作所面向服务器等产品开发出了在利用SRAM的同时还能省电的技术。SRAM方面,虽然可实现省电和高速化的电路细微化技术取得了发展,但是达到一定程度后很容易出现信号误差,导致SRAM的性能出现下降。过去通过施加高电压将信号误差几乎控制为零,不过该技术会影响省电效果。

日立转变了一直以来的思考方式,容忍可忽略的误差发生,开发出了可抑制SRMA驱动电源的设计方法。与系统控制有关的重要处理方面,通过软件来维持驱动电压,计算处理则根据事先设定的误差率来下调电压。

据称采用该方法计算机也能正常工作。预计还可以用于图像处理等。在模拟试验中,容忍5%的误差率的情况下,可将耗电量削减20%左右。

据称这一误差率在人观看图像时感觉不到图像出现劣化的范围内。日立计划20年将该方法推向实用,这将有助于信息社会的基础设施数据中心的节能化。

另一方面,由富士通和三菱电机等10家厂商组成的的超低电压装置技术研究联盟开发出了面向构成MRAM的记忆元件的微细加工技术。具体来说,首先制作出直径为35纳米(1纳米为10亿分之1米)的圆形元件,之后使元件周围氧化,将元件工作部分直径缩小至20纳米。

尽管微细化对实现省电有效,但是加工起来十分困难。据称相比一开始就将元件加工为直径20纳米,新技术的精确度更高、成本也更低。加入研究联盟的各厂商计划为高性能MRAM的实用化做出贡献。

版权声明:日本经济新闻社版权所有,未经授权不得转载或部分复制,违者必究。

报道评论